AMD va fournir un correctif qui améliore la latence inter-cœurs et les chipsets du Ryzen 9000 « Zen 5 »

Selon certaines informations, AMD travaillerait sur un nouveau correctif du BIOS qui contribuera à améliorer la latence inter-cœurs sur les processeurs de bureau Ryzen 9000 « Zen 5 ».

Les processeurs AMD Ryzen 9000 « Zen 5 » bénéficieront de nouvelles améliorations alors que Red Team prévoit de déployer un correctif du BIOS pour améliorer les latences inter-cœurs

Les processeurs de bureau Ryzen 9000 d'AMD basés sur Zen 5 n'ont pas fourni l'amélioration des performances que nous attendions tous. Même si l'une des raisons peut être attribuée aux mauvaises optimisations pour Windows 11, ce n'est pas la seule raison. Le Core Parking non optimisé est l'un des coupables qui entraîne des performances plus lentes que l'idéal, soi-disant en raison du logiciel inachevé et du support du BIOS.

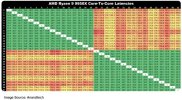

Dans l'évaluation d'Anandtech sur le Ryzen 9 9950X, il a été constaté que le processeur Zen 5 avait une latence inter-CCD nettement supérieure à celle de son prédécesseur. Et ce, malgré le fait que les processeurs Zen 4 et Zen 5 partagent une matrice d'E/S et une conception Infinity Fabric similaires. Cependant, un rapport récent de Geekerwan chez Bilibili (via @9950pro) suggère qu'AMD travaille à résoudre ce problème via un futur correctif du BIOS.

La latence inter-CCD correspond à la vitesse à laquelle les données ou les instructions sont transférées entre les deux CCD Zen 5 (Core Complex Dies) au sein des processeurs Ryzen 9000. Cette structure est utilisée pour la communication avec plusieurs chipsets tels que les CCD et les IOD. Comme les Ryzen 9 9950X et Ryzen 9 9900X contiennent deux CCD, chacun comportant 8 cœurs Zen 5, les programmes qui utilisent plus de 8 cœurs doivent transférer les données entre les CCD pour une exécution plus rapide.

Malheureusement, contrairement à son prédécesseur Ryzen 9 7950X, l'AMD Ryzen 9 9950X a une latence CCD à CCD presque deux fois supérieure à celle du premier. La latence inter-CCD moyenne pour Zen 5 est en moyenne de 180 ns contre 76 ns pour le 7950X. Cela entraîne un transfert de données plus lent entre les CCD, ce qui entraîne des performances multithread plus lentes que prévu dans certaines charges de travail.

La latence inter-CCD plus élevée n'est pas due à la conception de la puce, mais aux optimisations inachevées et non polies d'AMD au sein du BIOS et de la pile logicielle du chipset. Comme le suggère le nouveau rapport, AMD corrigera la latence inter-CCD élevée via une mise à jour du BIOS qui devrait être déployée dans les mois à venir.

Nous espérons que nous verrons des gains de performances avec la nouvelle mise à jour, mais la date exacte de la mise à jour du BIOS n'est pas encore connue. Ce correctif n'affectera cependant pas nécessairement les performances de jeu, car la plupart des jeux n'utilisent pas plus d'un CCD contenant huit cœurs. Dans les programmes qui peuvent utiliser plus de huit cœurs, le correctif de la latence inter-CCD peut résoudre certains problèmes de performances.

Pas plus tard qu'hier, AMD a annoncé qu'il apportait des optimisations de prédiction de branche à Windows 11 23H2 via le rétroportage, ce qui entraînera une amélioration des performances comme on le voit avec Windows 11 24H2. Il est donc évident qu’AMD s’est probablement précipité pour lancer une série Ryzen 9000 inachevée, qui nécessite davantage d’optimisations pour offrir des améliorations générationnelles significatives.

WCCFTECH

Après le correctif de Windows (pas transcendant en bench chez moi mais après avoir testé avec quelques jeux, c’est vrai qu'il y a du mieux), du tout bon pour nos proc' Rouges !

Après le correctif de Windows (pas transcendant en bench chez moi mais après avoir testé avec quelques jeux, c’est vrai qu'il y a du mieux), du tout bon pour nos proc' Rouges !